バンドオフセットの第一原理計算とTCADの連携:ヘテロ接合素子のバンドダイアグラム#

半導体デバイスの微細化・高性能化において、異種半導体接合(ヘテロ接合)界面の設計は極めて重要です。特に、高電子移動度トランジスタ(HEMT)などのデバイスでは、界面に形成される2次元電子ガス(2DEG)が高速動作の鍵を握ります。本事例では、第一原理計算ソフトウェアAdvance/PHASEを用いて算出したGaAs/AlAs界面の「バンドオフセット値」を物理パラメータとして用い、自作のPythonベース1次元TCAD(ポアソン方程式ソルバー)と連携させるマルチスケール解析のアプローチを紹介します。

Keywords: 第一原理計算(DFT), TCAD連携, ヘテロ接合, GaAs/AlAs, バンドオフセット, 2次元電子ガス (2DEG), HEMT

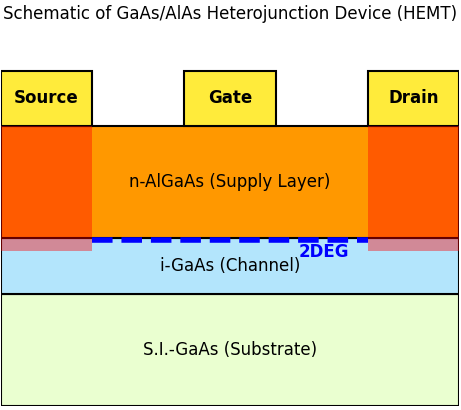

1. デバイス構造の模式図と解析の目的#

解析対象となるGaAs/AlAs系HEMTのデバイス構造模式図を図1に示します。三村らの原著論文 [1] では、材料としてGaAs/n-AlxGa1-xAsヘテロ接合が用いられていますが、本事例ではその物理的本質を検討するため、界面における基本構成であるGaAs/AlAsに注目して解析を行っています。電子供給層(n-AlGaAs)からチャネル層(i-GaAs)へ電子が供給され、界面のバンド不連続性によって薄い領域に高濃度の電子が局在します(2DEG)。本解析の目的は、このミクロな界面のバンドオフセット(第一原理計算)から、マクロなデバイス内部のキャリア分布(TCAD)を算出することです。

図1. 解析対象のHEMTデバイス構造模式図 (n: n型、i: intrinsic, S.I.: semi-insulating)。ソース・ドレイン電極間に広がるGaAs/AlAs界面の2DEG形成領域に注目して解析を行います。

2. 理論背景と計算式#

第一原理計算によるバンドオフセット#

既存の解析事例 [2]では、Advance/PHASEを用いた層分割状態密度(LayerDOS)の解析とシザー演算子法を組み合わせることで、GaAs/AlAs界面のバンドオフセットを導出しました。得られた伝導帯オフセット および価電子帯オフセット の値は以下の通りです。

- 伝導帯オフセット: eV (GaAs側が低い)

- 価電子帯オフセット: eV (GaAs側が高い)

TCADによる非線形ポアソン方程式の求解#

デバイス内部の静電ポテンシャル とキャリア分布は、以下の非線形1次元ポアソン方程式に従います [3, 4]。本事例ではこれを有限差分法とニュートン・ラフソン法を用いて自己無撞着(セルフコンシステント)に解きました。

上式における各変数の意味は以下の通りです。

- : 位置 における半導体の誘電率(本解析ではGaAsとAlAsで異なる値を設定)

- : 静電ポテンシャル(エネルギーバンドの曲がり具合に対応)

- : 素電荷(電子1個が持つ電荷の絶対値)

- : 正孔(ホール)密度、および電子密度(これらはポテンシャル に依存して指数関数的に変化するため、方程式が「非線形」となります)

- : イオン化したドナー濃度、およびアクセプタ濃度

電子密度 は、ボルツマン近似に従い、伝導帯有効状態密度 と静電ポテンシャルから定まる伝導帯エネルギー を用いて、 として算出されます。

ここで、第一原理計算によって得られた伝導帯オフセット は、TCADソルバー内において各材料の「電子親和力(Electron Affinity)」の空間的に変化する材料パラメータとして電荷項の計算に直接組み込まれます。

3. 計算手順とパラメーター設定#

Pythonで実装したTCADソルバーに、第一原理計算からの出力とマクロな材料パラメータを設定しました。本解析では、HEMTデバイスの核心である「チャネル層への不純物ドーピングが2DEGに与える影響」を評価するため、GaAs層のアクセプタ濃度()を変えた2つのケースを比較します。

表1. デバイスシミュレーション計算条件

| パラメータ | GaAs層 (チャネル層) | AlAs層 (電子供給層) |

|---|---|---|

| バンドギャップ () | 1.43 eV | 2.16 eV |

| 伝導帯オフセット () | (基準) | -0.23 eV (DFT算出値) |

| 比誘電率 () | 12.9 | 10.06 |

| ドナー濃度 () | - | cm |

| アクセプタ濃度 () | Case A: cm (p型ドープ) Case B: cm (極低濃度) |

- |

4. 計算結果の詳しい説明と考察#

TCADシミュレーションにより、チャネル層のドーピング濃度がバンドの曲がり(バンドベンディング)と電子密度に与える劇的な影響が確認されました。

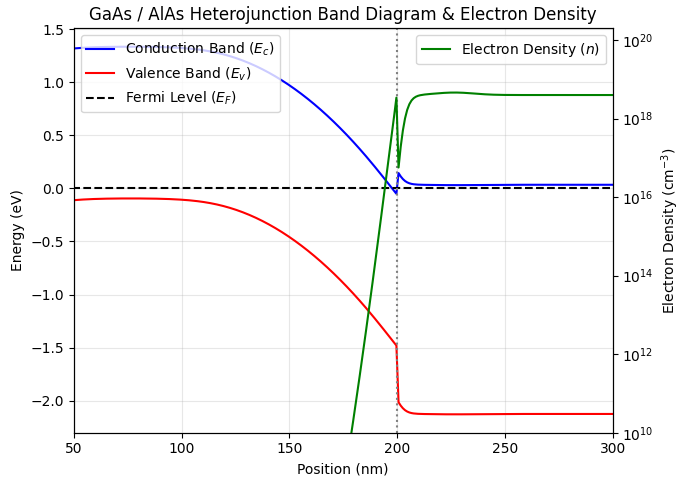

Case A: チャネル層をp型ドープした場合#

まず、GaAs層に意図的にp型不純物をドープした場合( cm)の計算結果を図2に示します。

図2. 高濃度ドープ時のバンドダイアグラム(x < 200nm:GaAs側、x > 200nm:AlAs側、x = 200nm:界面)。アクセプタの影響でノッチが浅くなり、電子密度(緑線)が十分に高まっていません。

【考察】

界面に伝導帯の落ち込み(ノッチ)は形成されていますが、2DEGの電子密度は cm クラスにとどまっています。これは、GaAs側に多量のアクセプタが存在するため、熱平衡状態においてバンド全体が上方(正孔側)へ強く引っ張り上げられ、ノッチの底がフェルミ準位(、黒破線)に対して十分に深く沈み込まないためです。また、不純物濃度が高いために空乏層が狭く、GaAs側の深部(グラフ左側)ではバンドが速やかに平坦化(フラットな状態)している様子が確認できます。

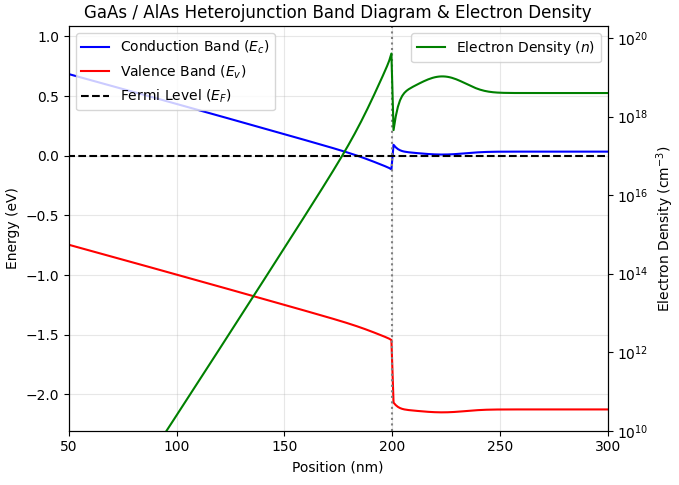

Case B: チャネル層を極低濃度(i-GaAs)にした場合#

次に、実際のHEMT設計と同様に、GaAs層を不純物のほとんどない真性半導体(i-GaAs, cm)に近づけた場合の結果を図3に示します。

図3. 低濃度ドープ時のバンドダイアグラム(x < 200nm:GaAs側、x > 200nm:AlAs側、x = 200nm:界面)。深いノッチが形成され、高濃度な2DEGが蓄積しています。

【考察】

GaAs側の不純物濃度を下げたにもかかわらず、界面における電子密度(緑線)は cm レベルにまで劇的に増加しています。これは、不純物によるバンドの押し上げ効果がなくなり、第一原理計算から導かれた eV のポテンシャル障壁がそのまま深い「井戸(ウェル)」としてフェルミ準位の下に沈み込むためです。このとき、不純物が非常に少ないために空乏層がチャネル層全体に広がり、GaAs側(グラフ左側)のバンドが基板方向へ向かって緩やかな斜め(傾斜)状の分布を示しているのが、Case Aとの物理的な大きな違いです。

第一原理計算とTCAD連携によるHEMT設計の裏付け

HEMTの核心的なアイデアは、電子を供給するドナー不純物と、実際に電子が走行するチャネルを空間的に分離し、不純物散乱を排除することで高い電子移動度(High Electron Mobility)を実現することにあります。

しかし、チャネル層に不純物をドープしなくても、十分に高い濃度の電子を蓄積できるのでしょうか? 本事例のシミュレーションは、まさにその疑問を静電的な観点から検証したものです。第一原理計算によって算出した正確なバンドオフセット値を入力しTCADで解析した結果、チャネルに不純物をドープした場合(Case A)は静電的にバンドが持ち上がり、かえって2DEG濃度が低下してしまうことが示されました。一方で、チャネルを低濃度(i-GaAs)にした場合(Case B)は、深いポテンシャル井戸が維持され、不純物散乱のない領域に高濃度な2DEGを蓄積できることが定量的に確認されました。

つまり、このマルチスケール解析は、「高移動度を得るためにチャネルをi-GaAsにする」というHEMTの設計原理が、キャリア蓄積の観点からも合理的であることを裏付けています。実際のデバイス開発における3次元構造等の高度な解析には、統合TCADシステム「Advance/TCAD」のような専用ソフトウェアの使用が推奨されます。

まとめ#

本事例では、第一原理計算ソフトウェアAdvance/PHASEで得られたGaAs/AlAs界面のバンドオフセット値を入力として、Pythonを用いた1次元TCADシミュレーションを実行しました。「原子レベルの電子状態計算」と「マクロなポアソン方程式の求解」を連携させることで、HEMT特有のバンドベンディングや2DEGの形成を、理論的根拠に基づいて定量的に可視化できることを示しました。

本解析の詳細や、研究への適用可能性に関するご相談はこちら

お問い合わせ参考文献#

- T. Mimura, S. Hiyamizu, T. Fujii, and K. Nanbu, "A New Field-Effect Transistor with Selectively Doped GaAs/n-AlxGa1-xAs Heterojunctions", Jpn. J. Appl. Phys. 19, L225 (1980).

- 異種半導体接合界面におけるバンドオフセットの第一原理計算:GaAs/AlAsの例

- S. M. Sze, Y. Li, and K. K. Ng, Physics of Semiconductor Devices, 4th ed., Wiley (2021).

- S. Selberherr, Analysis and Simulation of Semiconductor Devices, Springer-Verlag (1984).

関連ページ#

- 第一原理計算ソフトウェア Advance/PHASE

- 解析分野:ナノ・バイオ

- 産業分野:材料・化学