異種半導体接合界面におけるバンドオフセットの第一原理計算:GaAs/AlAsの例#

半導体デバイスの微細化に伴い、材料の特性を巨視的なモデルだけでなく、原子・分子レベルから詳細に調べる必要性が高まっています。特に、異種半導体接合界面における「バンドオフセット」は、接合体におけるキャリア分布の設計において重要な物性値です。本解析事例では、第一原理計算ソフトウェアAdvance/PHASE を用いて、代表的な化合物半導体であるGaAs/AlAs界面のバンドオフセットを計算し、マクロなデバイスシミュレーションの入力値として活用するための、実践的な解析アプローチを紹介します。

Keywords: バンドオフセット, 第一原理計算 (DFT), ヘテロ接合, GaAs/AlAs, 層分割状態密度 (LayerDOS), シザー演算子法, バンドギャップ問題

背景と計算モデル#

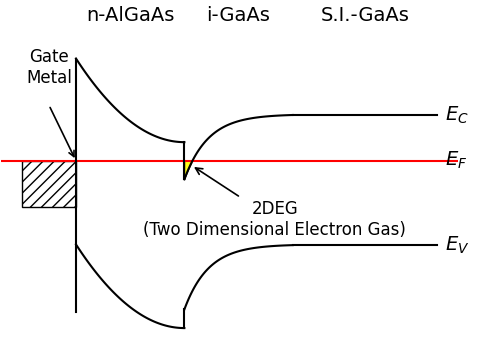

異種半導体界面では、物質間のバンドギャップの違いにより、伝導帯と価電子帯にそれぞれエネルギー準位の不連続性(オフセット)が生じます [1]。図1は、デバイスでよく見られるGaAs/AlAs系(n-AlGaAs / i-GaAs / S.I.-GaAs)のヘテロ接合におけるバンドベンディングと二次元電子ガス(2DEG)形成の模式図です。このような挙動を正確に把握するためには、各材料間のバンドオフセットを第一原理計算から正確に求めることが重要になります。

図1. n-AlGaAs/i-GaAs/S.I.-GaAs ヘテロ接合におけるバンドオフセットと2DEG形成の模式図 (n: n型、i: intrinsic, S.I.: semi-insulating)。

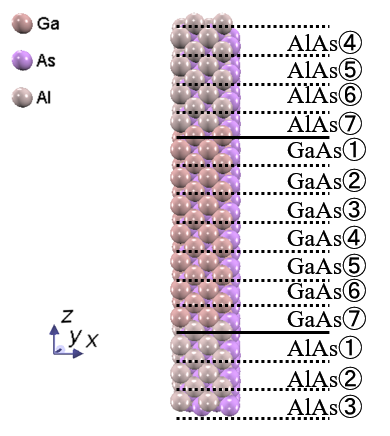

本解析における計算モデルとして、GaAsとAlAsの接合界面を模擬したスーパーセルを作成しました(図2)。計算の詳細は以下の通りです。

- 境界条件: x, y, z方向に周期的境界条件を適用。

- 格子定数: 両物質の格子整合を仮定し、基板となるGaAsの格子定数(5.682 Å)を採用しています(AlAs単体の格子定数は5.731 Å)。

- セル構造: 計算ユニットセル内に2つの界面を持ち、z方向にそれぞれ7層分(7倍周期)の厚みを持たせたスーパーセルモデルを使用しました。

図2. GaAs/AlAs界面のスーパーセル計算モデル。両物質それぞれ7層分の厚みを持ちます。

計算手順と状態密度(LayerDOS)の解析#

バンドオフセットは、界面から十分に離れた両物質の「バルク領域」におけるエネルギー準位の相対差から求めます。構築したGaAs/AlAsスーパーセルモデルに対してDFT計算を実行し、各層ごとの「層分割部分状態密度(Layer DOS)」を出力しました。

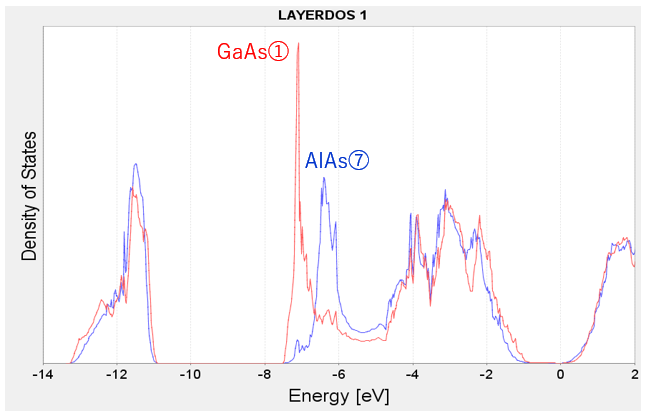

図3. 界面近傍(GaAs①とAlAs⑦)のLayerDOS。軌道混成の影響が見られます。

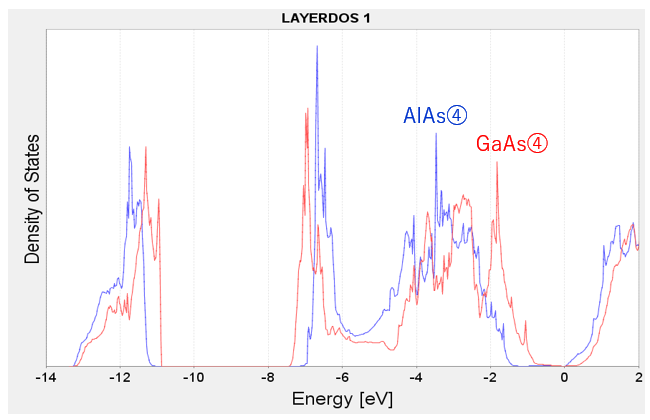

図4. バルク領域(GaAs④とAlAs④)のLayerDOS。バルクの性質を反映しています。

バンドオフセットは界面領域(図3)ではなく、界面から離れた中央領域のバルク層(図4)の状態密度を比較し、両者の価電子帯上端(VBM)および伝導帯下端(CBM)のエネルギー差を読み取ることで、オフセット値を算出します。

計算結果#

標準的なDFT汎関数による課題#

標準的なGGA汎関数(PBEなど)を用いて算出した結果、AlAsを基準としたGaAsの価電子帯オフセット(VBO)は+0.5 eVと得られました。しかし、図4のLayerDOS(バルク領域)を見ると、伝導帯下端(CBM)のエネルギー位置に関してもGaAs側が高く算出されており、このままでは本来の物理的挙動と矛盾が生じます。

この矛盾の根本的な原因は、密度汎関数理論(DFT)における「バンドギャップの過小評価問題」にあります。バンドギャップが過小評価される度合いは材料や計算条件によって大きく変動します。今回の計算では、各物質のバンドギャップが正しく再現されなかった結果、本来はGaAsのバンドがAlAsのギャップ内に収まる「Type-I型」であるはずが、計算上は伝導帯の順序が逆転したような配列となってしまいました。そのため、標準的なDFTによる計算値をそのままデバイスシミュレーションなどの設計値として採用することは困難です。

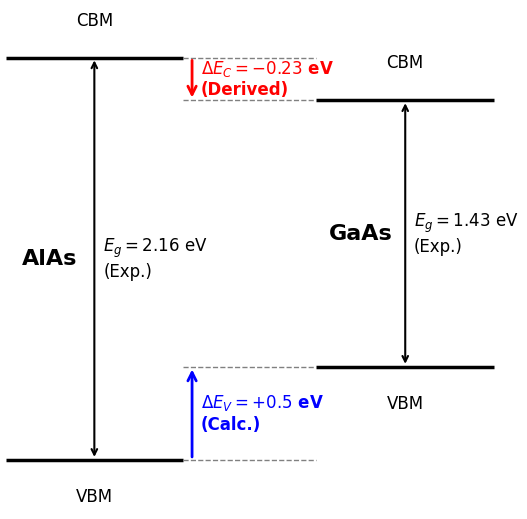

シザー演算子法による伝導帯オフセットの推算#

標準的なDFT計算では伝導帯の予測精度に課題がありますが、一方で電子が占有している価電子帯(VBM)の相対的な位置関係については、実用的な精度で計算できることが知られています。そこで、計算で得られた「価電子帯オフセット」を基準とし、そこに「実験値のバンドギャップ」を適用して伝導帯の相対位置を推算するアプローチ(シザー演算子法)が、実務において有効です [2]。

本計算結果(VBO = +0.5 eV)と実験値を用いた補正手順は図5の通りです。

図5. 第一原理計算による価電子帯オフセット(青)と実験値バンドギャップ(黒)から、伝導帯オフセット(赤)を推算するロジック図

この補正によって、「GaAsのVBMが0.5 eV高く、CBMが0.23 eV低い(AlAsを基準として eV)」という関係性が導かれました。これにより、実際のデバイスで観測される正しい「Type-I型ヘテロ接合」のバンド配列を再現することができました。このようにバンドギャップの計算誤差の影響を実験値で切り分けることで、実用的なオフセット値を導出することが可能です。なお、本計算で得られた価電子帯オフセット(+0.5 eV)は、全電子計算を用いた先行研究による理論値(+0.51 eV)[2]と良好に一致しており、本解析アプローチの妥当性を裏付ける結果と言えます。

Hybrid汎関数(HSE06)への展開#

既知の材料であればバンドギャップの実験値を用いた補正が可能ですが、新規材料開発においては物性の予測そのものが困難になります。このバンドギャップ問題を解決し、より正確なバンドオフセットを予測するためには、厳密交換相互作用を取り入れたHybrid汎関数(HSE06など)[3] の使用が有力です。HSE06汎関数を用いることで計算コストは非常に増大しますが、実験値に近いバンドギャップを第一原理計算から直接求めることが可能になります [4]。

まとめ#

本事例では、第一原理計算ソフトウェアAdvance/PHASEを用いた異種半導体界面(GaAs/AlAs)のバンドオフセット計算を検証しました。標準的なGGA汎関数ではバンドギャップの過小評価問題により正確なオフセットを直接見積もることは困難ですが、LayerDOSから得られる価電子帯の相対位置とバンドギャップの実験値を組み合わせることで実用的な推算が可能です。さらに、新規半導体材料開発に向けて実験値を用いずに定量的な予測を行うためには、HSE06をはじめとするハイブリッド汎関数の適用が有効な手段となります。

本解析の詳細や、研究への適用可能性に関するご相談はこちら

お問い合わせ参考文献#

- C. G. Van de Walle and R. M. Martin, "Theoretical study of band offsets at semiconductor interfaces", Phys. Rev. B 35, 8154 (1987).

- S. H. Wei and A. Zunger, "Calculated natural band offsets of all II–VI and III–V semiconductors: Chemical trends and the role of cation d orbitals", Appl. Phys. Lett. 72, 2011 (1998).

- J. Heyd, G. E. Scuseria, and M. Ernzerhof, "Hybrid functionals based on a screened Coulomb potential", J. Chem. Phys. 118, 8207 (2003).

- ハイブリッド汎関数法を用いた半導体のバンドギャップ計算

関連ページ#

- 第一原理計算ソフトウェア Advance/PHASE

- 解析分野:ナノ・バイオ

- 産業分野:材料・化学