SRAMソフトエラーのデバイスシミュレーション#

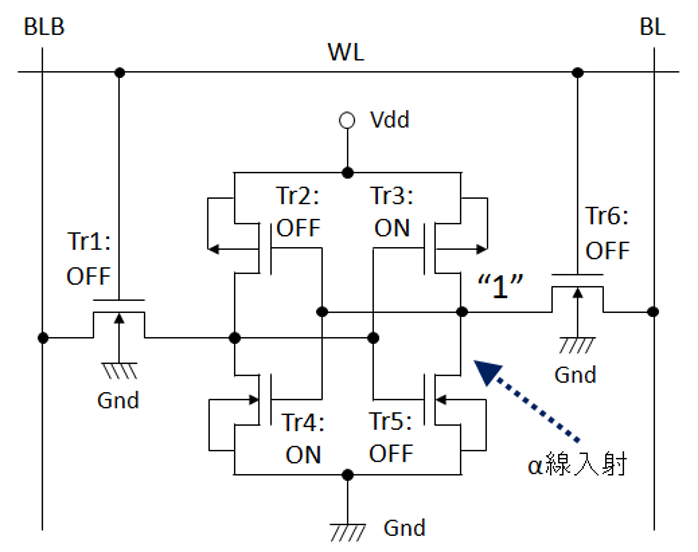

SRAMソフトエラーの原理#

-

SRAMのインバータ出力部の拡散層付近にα線が入射し、電子・正孔対が発生する。

-

pnジャンクション近傍で発生した電子と正孔は、ドリフト・拡散により、それぞれn型とp型領域に移動する。

-

インバータの出力部に移動してくる電子や正孔による電位でビットが反転した場合、ソフトエラーとなる。図ではビット“1”から”0”に反転する。

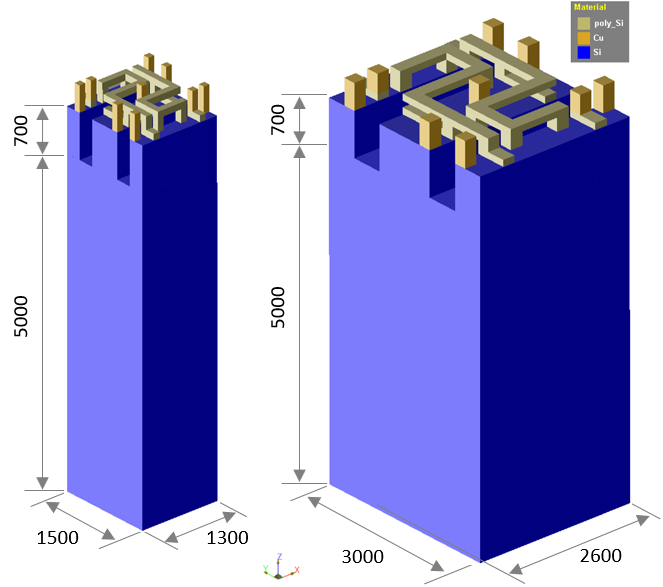

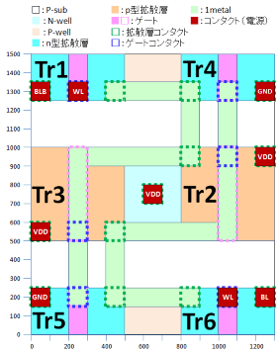

デバイスシミュレーションの解析モデル#

-

6個のトランジスタと2本の配線を1つのデバイスシミュレーションモデルとして作成した。

-

L=100nmとL=200nmのゲート酸化膜厚は、それぞれ5nmと10nmとした。

-

L=100nmのモデルの基板、p-well、n-wellの不純物濃度はL=200nmのモデルの2倍に設定した。

デバイスシミュレーション解析条件#

| 解析条件 | 解析モデル | α線の入射エネルギー[MeV] |

|---|---|---|

| 1 | L=100nm | 0.057 |

| 2 | L=100nm | 0.696 |

| 3 | L=200nm | 0.696 |

| 4 | L=200nm | 0.865 |

-

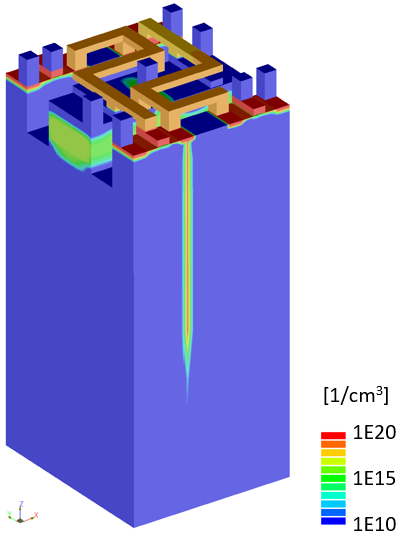

α線がTr5のドレイン側拡散層に真上から入射したと仮定し、入射エネルギーに応じて電子・正孔対を配置した。

-

一対の電子・正孔対を発生させるのに3.6eVが必要であるとして発生個数を概算した。

-

Siの電子的阻止能を2.094×10^3 (MeV/cm)として、 α線の侵入深さを概算した。

計算結果#

-

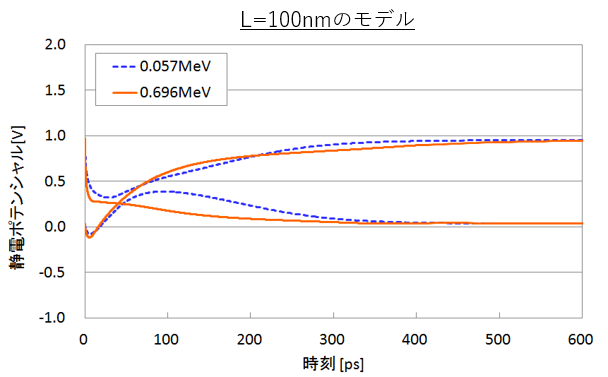

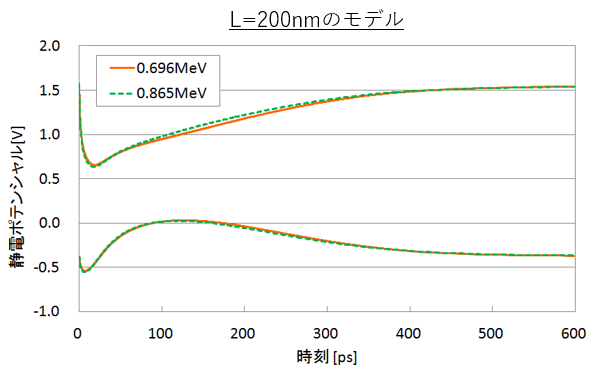

L=100nmでE=0.696MeVの場合にはインバータの出力電位の静電ポテンシャルの大小が逆転し、ソフトエラーとなった。

-

それ以外の場合には二つのインバータの出力部の静電ポテンシャルの差は、途中までは小さくなったが逆転するまでには至らず、元のビット“1”の定常状態に戻った。

-

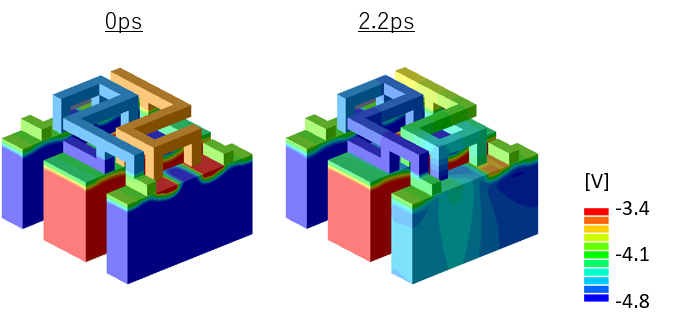

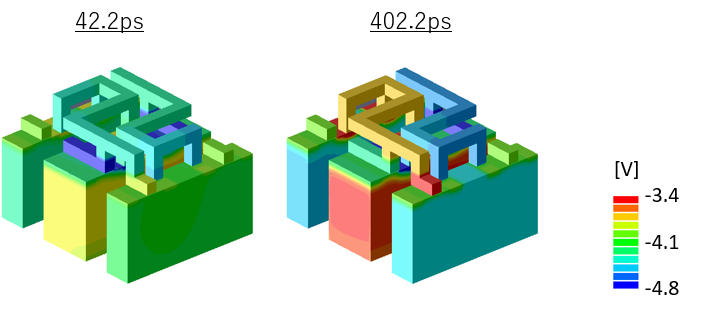

時間が進むにつれ、2つの配線およびインバータのゲートの電位の大小が反転していく。

-

このように、デバイスシミュレーションで解析したことにより、デバイス全体の静電ポテンシャル分布の時間変化が解析可能となる。

関連ページ#

- 半導体デバイス3次元TCADシステム Advance/TCAD

- 解析分野:半導体デバイス

- 産業分野:エレクトロニクス